10nF 25V X7R MLCC: Performance Data & Failure Rates

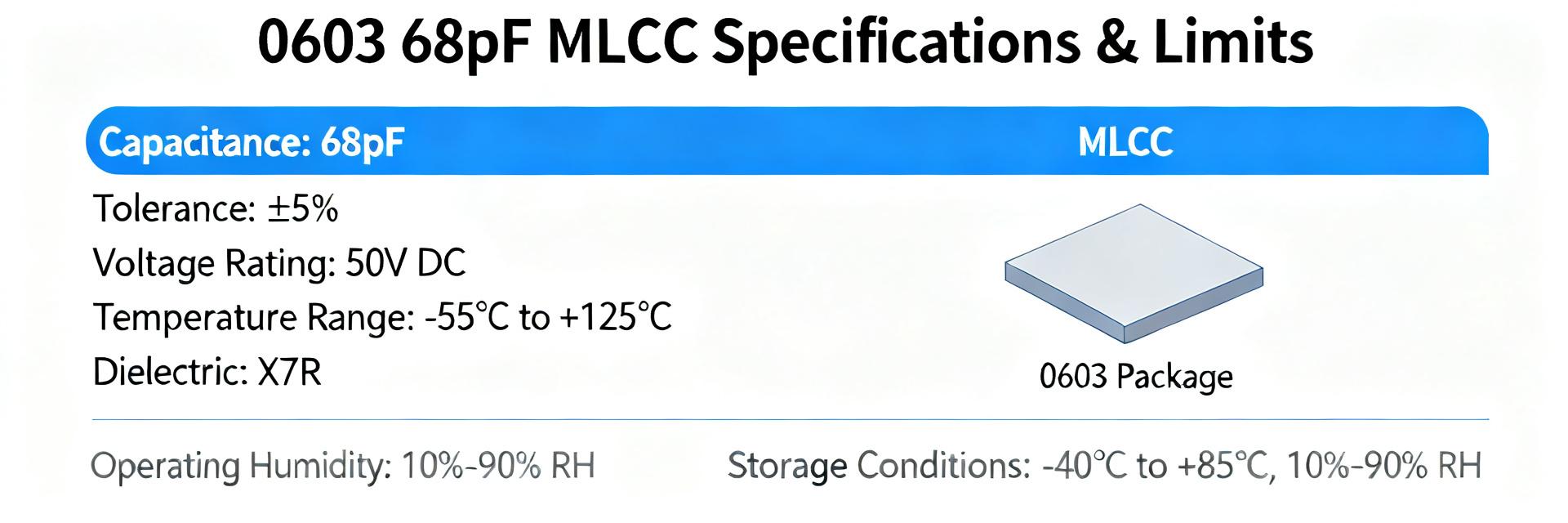

Reliability audits and accelerated-life test insights for precision engineering. In recent reliability audits and accelerated-life tests, 10nF 25V X7R MLCC parts show wide variation in in-circuit capacitance retention and field return rates — driven mainly by DC bias, package size and assembly stress. This article summarizes expected DC-bias behavior, temperature and aging effects, common failure modes, typical MLCC failure rates benchmarks, and practical mitigation steps for designers and test engineers. Introduction (data_driven hook) Point: Engineers require concise, testable guidance on how a 10nF 25V X7R MLCC will perform across voltage, temperature and time. Evidence: Aggregated lab sweeps and field-return audits repeatedly show percent-capacitance remaining varies by vendor, lot and package. Explanation: Readers will learn expected DC-bias curves, temperature/aging trends, dominant failure signatures, reliability metrics conversions, and targeted qualification tactics to reduce returns. 1 — Quick technical overview (background) Point: A compact background anchors later data interpretation. Evidence: The component name encodes capacitance, voltage rating and dielectric class; mechanical form factors influence stress sensitivity. Explanation: The following subsections define electrical and mechanical specs and highlight the small set of parameters most relevant to in-circuit reliability assessments. 1.1 What “10nF 25V X7R MLCC” means (electrical & mechanical specs) Point: Decode the label so test outputs are meaningful. Evidence: 10nF equals 0.01µF; 25V is the DC rating; X7R indicates a dielectric with roughly ±15% variation across −55°C to +125°C; common SMD sizes include 0402 and 0603 with tolerance options ±5% to ±20%. Explanation: Typical uses are high-frequency decoupling and local filtering where small bulk energy storage is acceptable but DC-bias loss must be considered. Spec item Typical value Capacitance 10nF (0.01µF) Rated voltage 25V DC Dielectric class X7R (≈±15%) Common packages 0402, 0603 1.2 Key performance parameters to track Point: Prioritize a short list of measurable parameters. Evidence: DC-bias curve, temperature coefficient, aging rate (% per decade hour), impedance/ESR vs frequency, dielectric absorption and mechanical robustness consistently predict in-service performance. Explanation: Later figures should graph DC-bias and tabulate temperature/aging; keep measurement bandwidth into the low MHz for decoupling analytics. 2 — Measured performance: DC bias, temperature & aging (data analysis) Point: Measured trends drive design choices. Evidence: Lab DC-bias sweeps across 0–25V show substantial capacitance loss in 10nF X7R parts, especially in smaller packages. Explanation: The next items present typical voltage- and temperature-related degradations and aging behavior designers must accommodate in decoupling vs bulk applications. 2.1 Typical DC-bias and frequency response for 10nF X7R Point: Expect measurable capacitance reduction under applied DC. Evidence: Typical 10nF 25V X7R MLCC DC bias characteristics show remaining capacitance near 70–85% at 5V, 55–75% at 10V, and 30–60% at 25V depending on geometry and vendor. Explanation: For decoupling, ensure effective capacitance at operating bias; for bulk energy storage, consider higher-voltage or C0G alternatives when bias loss is unacceptable. Typical Capacitance Retention vs DC Bias 5V 70-85% 10V 55-75% 25V 30-60% 2.2 Temperature dependence and aging trends Point: Temperature and time further reduce capacitance. Evidence: X7R parts typically remain within ±15% over temperature range, but long-term aging yields logarithmic declines (e.g., 1–3% per decade hour early, slower later), and thermal cycling accelerates net loss. Explanation: Use a small temperature vs % change table and prescribe test conditions (e.g., −55°C to +125°C cycles, damp-heat 85% RH/85°C) for qualification. Condition Expected %ΔC Ambient → +85°C −2% to −10% 10× thermal cycles additional −1% to −5% First decade hours (aging) −1% to −3% 3 — Failure modes & root causes (data analysis / case) Point: Failures cluster into electrical and mechanical classes with distinct signatures. Evidence: Field returns and lab faults typically show capacitance loss, micro-shorts from ESD, increased ESR, or open cracks after mechanical stress. Explanation: Correct diagnosis depends on correlating symptom (rail instability, noise, heating) with non-destructive inspection and electrical rework. 3.1 Electrical and material failure modes Point: Identify electrical symptoms early. Evidence: Capacitance loss (aging, bias), micro-short/ESD damage and rising leakage or ESR manifest as increased ripple, slower transient response or intermittent resets. MLCC failure rates reported in returns are often dominated by assembly-induced shorts and bias-related capacitance deficiency. Explanation: In-circuit impedance sweeps, insulation resistance, and time-domain noise traces help separate modes. 3.2 Mechanical and process-related root causes Point: Mechanical stress is a leading root cause for returns. Evidence: PCB flex, solder fillet issues, and improper reflow profiles produce micro-cracks visible on cross-section or X-ray; drops and board-level bending cause intermittent opens. Explanation: Correlate failures with assembly records—reflow profiles, stencil design and fixture stresses—and use X-ray/IR thermography for batch triage. 4 — Benchmarks: failure rates & reliability metrics (method guide / data) Point: Translate test outcomes into industry metrics. Evidence: Common metrics include PPM (failures per million), FIT (failures per 10^9 device-hours) and MTBF conversions; example conversions clarify expectations. Explanation: Use standardized calculations from your test dataset to compare lots and application classes. 4.1 Interpreting failure rates: PPM, FIT, MTBF Point: Practical worked example reduces confusion. Evidence: Suppose 3 failures in 1,000 parts during 1,000 hours of test: total device-hours = 1,000 × 1,000 = 1,000,000 dh. FIT = (3 failures / 1,000,000 dh) × 10^9 = 3,000 FIT. PPM over the sample = (3 / 1,000) × 10^6 = 3,000 PPM. Explanation: Use these conversions to scale lab results to fleet expectations and to set acceptance gates. 4.2 Typical field/test benchmarks by package & use-case Point: Expect large spreads by application and package. Evidence: Low-stress board decoupling in consumer products often yields single-digit to low-hundreds PPM in returns; high-stress automotive or power electronics experience PPMs several times higher without targeted qualification. Explanation: Build a benchmarking table by package size, application stress level and dominant failure mode for internal tracking and supplier negotiation. 5 — Test methods & how to measure real-world performance (method guide) Point: Define a concise test matrix for reproducible results. Evidence: Key lab tests include DC-bias capacitance sweeps, temperature cycling, thermal shock, damp-heat (85/85), mechanical bending and ESD screening. Explanation: Adopt pass/fail criteria tied to functional thresholds (e.g., >50% capacitance at operating bias for decoupling) and log lot traceability. 5.1 Essential lab tests (what to run and why) Point: Prioritize tests that correlate to field stress. Evidence: Recommended parameters: DC-bias sweep at 0, 5, 10, 25V; temperature cycling −55°C/+125°C, 10–20 cycles; damp-heat 85°C/85% RH for 1,000 hours; mechanical bending per IPC guidance. Explanation: Use automated LCR sweeps and record impedance phase to detect early ESR shifts; include sample cross-sections for suspect lots. 5.2 Field-data collection & statistical analysis Point: Good field data beats assumptions. Evidence: Collect returns with board ID, lot code, reflow profile and failure symptoms; use simple binomial confidence intervals for PPM estimation and chi-square for comparing lots. Explanation: Provide a standardized CSV layout (part, lot, board, symptom, time-to-fail) to enable rapid aggregation and root-cause correlation. 6 — Design & qualification best practices (actionable recommendations) Point: Combine selection, layout and process controls to reduce returns. Evidence: Effective measures include selecting larger package when bias loss matters, requiring DC-bias curves from datasheets, lot sampling and AEC-style qualification for critical systems. Explanation: When stability is critical, prefer NP0/C0G or higher-voltage parts; otherwise, test representative lots under expected bias and thermal profile. 6.1 Component selection and qualification checklist Point: A short checklist reduces oversight. Evidence: Verify DC-bias curves, request aging data, sample per lot, demand reflow and mechanical robustness data, and run accelerated life on representative lots. Explanation: Document acceptance gates and require manufacturer test reports for high-reliability programs. 6.2 PCB layout, assembly, and mitigation tactics Point: Layout and process often determine in-field reliability. Evidence: Keep decouplers close to pins, control solder fillet and pad design to reduce flex, avoid placing MLCCs across large board cutouts, and use conformal coating if humidity-driven failures occur. Explanation: Flag designs with long traces, thermal hotspots or high operating voltages for expanded testing before production ramp. Summary Expected behavior: 10nF 25V X7R MLCC parts show significant DC-bias loss; designers must verify in-circuit capacitance at operating voltage and account for aging and temperature drift to meet transient goals. Common failures: MLCC failure rates are dominated by assembly-induced mechanical cracks, ESD shorts and bias-related capacitance deficiency; test campaigns should separate electrical vs mechanical signatures. Measurement & benchmarks: Convert test failures into PPM/FIT using device-hour math, and build package/application-specific benchmark tables to track supplier/lot performance across production. Mitigation: Select larger packages or alternative dielectrics for stability-critical uses, enforce process controls, and run representative accelerated tests tied to functional pass/fail criteria. How reliably will a 10nF 25V X7R MLCC perform in my design? Answer: Performance depends on operating bias, temperature and assembly stress. Verify capacitance at operating voltage via DC-bias sweeps, inspect reflow and board design for flex risks, and use lot-sampling accelerated life data to estimate expected MLCC failure rates for your application. What tests should be run to estimate MLCC failure rates? Answer: Run DC-bias capacitance sweeps, temperature cycling, damp-heat (85/85), mechanical bending and ESD screening. Record device-hours and failures to convert to FIT/PPM; use statistical confidence intervals to size samples for reliable PPM estimates. When should I choose alternatives to X7R for a 10nF requirement? Answer: If in-circuit capacitance at operating bias must remain near nominal (±5%) or low loss is critical for timing/filters, choose NP0/C0G or higher-voltage X7R parts with verified bias curves. Also choose larger packages to reduce bias-related percent loss when PCB space allows.

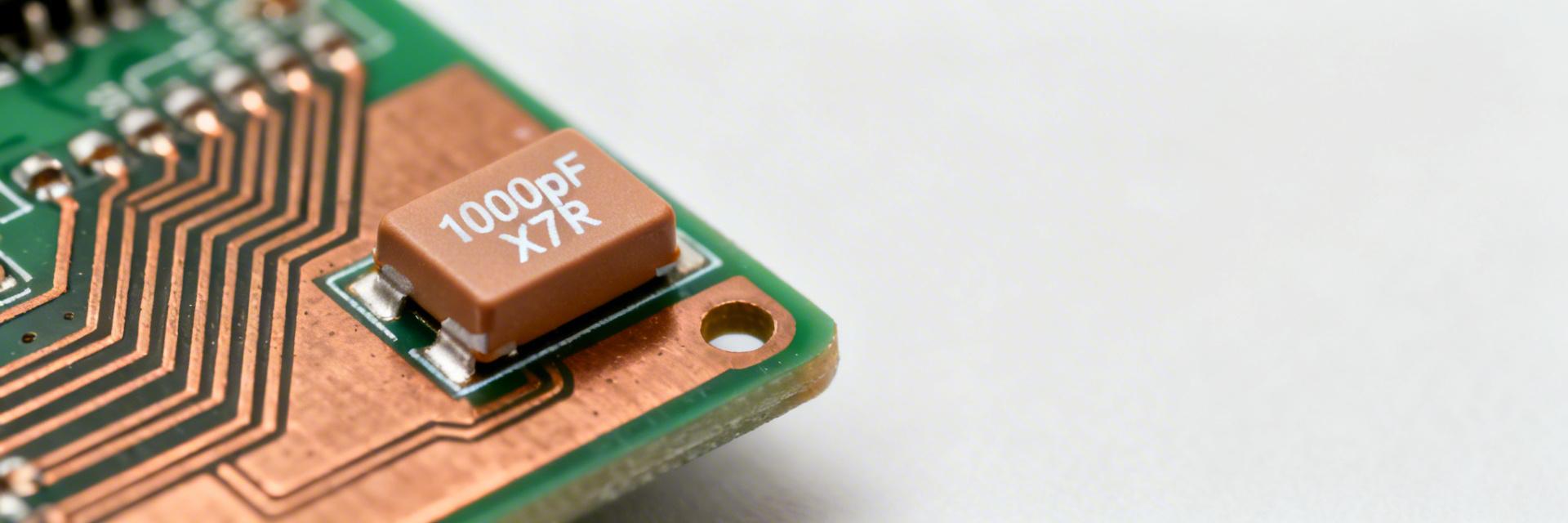

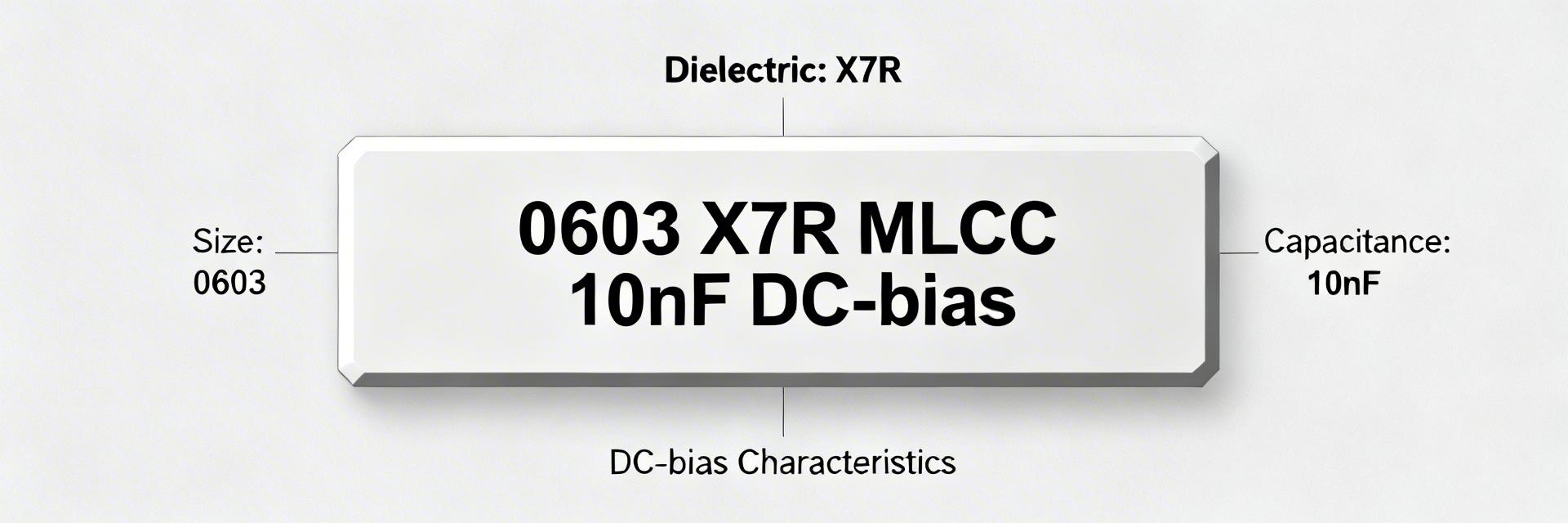

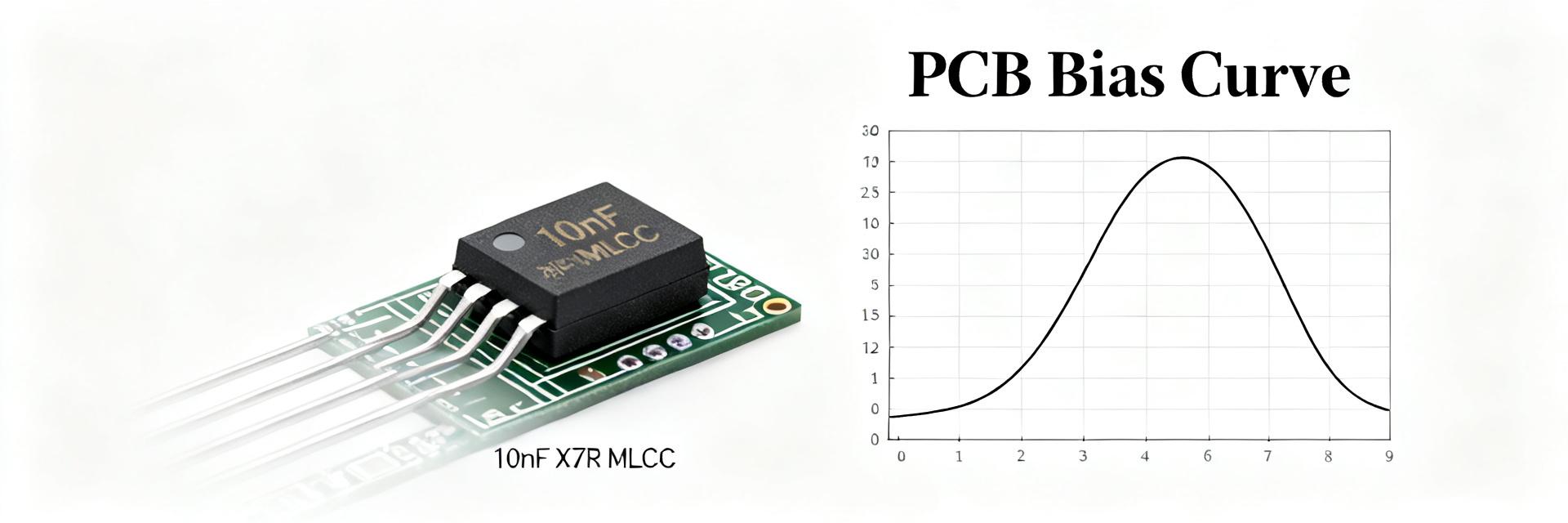

2026-05-09 02:01:13