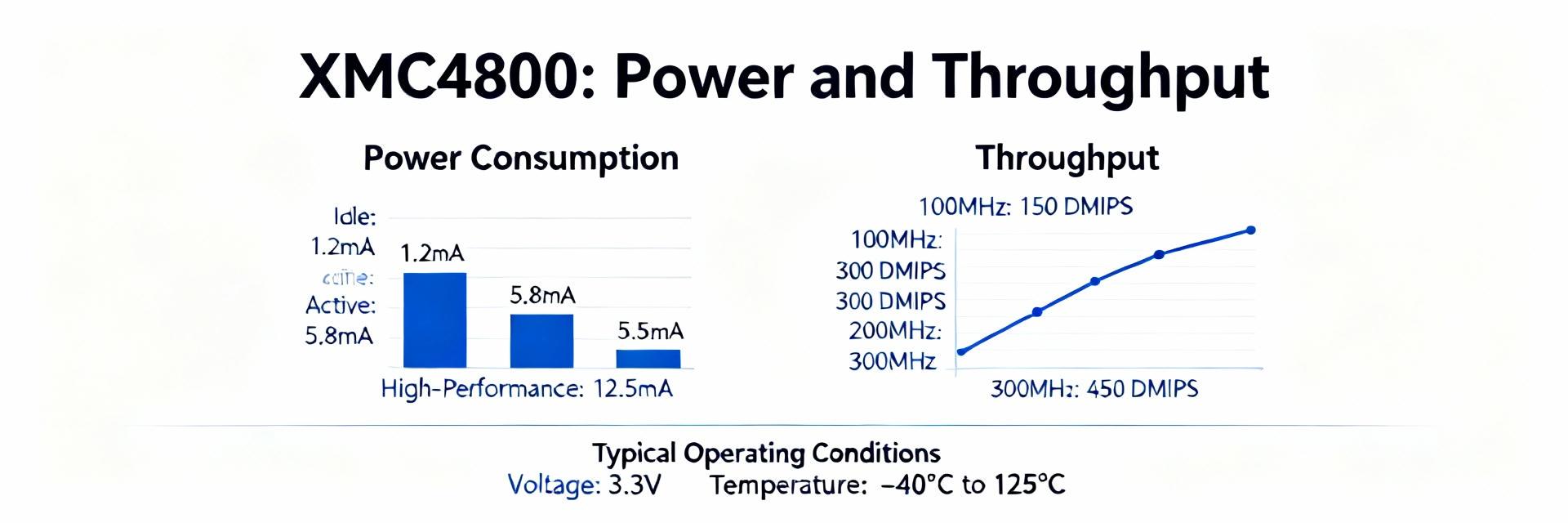

测量的性能和功率决定了32位工业MCU是否满足实际部署限制:基准套件与系统功率配置文件相结合,揭示了每瓦计算、输入/输出瓶颈和网络可行性。本文重点介绍受控CPU/内存/输入/输出基准、可重复功率测量、以太网和DMA吞吐量测试以及实用的调整建议xmc4800e196k2048最大功率1以指导工程权衡和部署选择。

介绍(数据驱动挂钩-文章的10-15%)

要点:工程师在MCU传感器聚合、协议桥接或边缘计算角色之前需要数字证据。证据:CoreMark/Dhrystone、memcpy微基准测试、DMA和以太网数据包测试以及microamp睡眠分析的组合可以获得完整的视图。说明:本文概述了受控测试、测量最佳实践和结果解释,以便团队可以评估实际工作负载下的延迟、MB和microjoules-per-operationxmc4800e196k2048最大功率1.

背景与关键规格(背景)

关键规格一览(闪存、SRAM、最大时钟、ADC通道、I/O、封装)

要点:关键硬件限制决定了基准测试的上限和功耗范围。证据:核心、闪存、SRAM、时钟和外设数量决定了可实现的CoreMark/MHz、DMA竞争和ADC采样吞吐量。解释:下表紧凑地展示了直接影响CPU、内存延迟和外设吞吐量的参数,便于在测试设计时快速参考。

| 规格 | 值(典型值) | 影响 |

|---|---|---|

| 闪光灯 | 2048KB | 闪存等待状态影响代码获取延迟和分支密集型工作负载 |

| 静态随机存取存储器 | ~352 KB (包装内) | 允许使用大缓冲区,减少外部内存流量 |

| 最大 CPU 时钟 | 最高可达144 MHz(器件数据表) | 除非I/O绑定,否则直接扩展CoreMark和吞吐量 |

| 核心 | 带FPU的Cortex-M4 | FPU提升FP内核吞吐量并减少周期计数 |

| 直接内存访问 | 多渠道 | 支持 memcpy 和外设突发传输的零 CPU 传输 |

| 通讯 | 以太网,SPI,UART,CAN | 确定网络和外围应力上限 |

影响性能的架构亮点

观点:架构特征在微基准测试中设置了可观察的瓶颈。证据包括FPU、总线矩阵、DMA引擎,以及闪存预取/加速变更周期/作和延迟。解释:浮点单元对浮点核产生了大量胜利;多主总线和独立的外设DMA可减少CPU卡顿;闪存等待状态或缓存缺失会增加指令取指的延迟,降低CoreMark/MHz,除非关键代码被迁移到SRAM。

基准方法和测试设置(数据分析)

测试环境和重复性

要点:可重复的测量需要受控的硬件、固件和日志记录。证据:使用标准的评估板或经过良好表征的载体,通过校准的分流器+ADC或高边电流表测量电流,并使用示波器/电流探头捕获瞬态行为。解释:锁定时钟设置、编译器优化和构建标志;记录环境温度和电源轨滤波;运行预热周期;以CSV格式记录结果,包含时间戳、测试ID和平均样本,以确保多次运行间的统计有效性。

工作负载、基准测试和测量指标

要点:一个代表性套件可以捕捉CPU、内存、中断和I/O行为。证据:将CoreMark和Dhrystone结合用于CPU基准,使用整数/浮点内核和memcpy用于内存,进行中断延迟测试以满足实时约束,以及使用DMA、SPI/UART突发和以太网数据包流用于I/O。解释:捕捉CoreMark/MHz、Dhrystone DMIPS、每操作的周期数、延迟(微秒)、DMA/以太网的MB/秒以及每操作的能耗(微焦耳),以实现跨平台规范化和能效比较。

CPU、内存和I/O基准测试结果(数据分析)

CPU性能:解释CoreMark / Dhrystone结果

要点:原始核心标记数字必须归一化才能显示真正的CPU能力。证据:在核心标记/兆赫旁边显示绝对核心标记,并报告闪存等待状态和使用的时钟设置。解释:跨时钟速率和闪存等待状态进行归一化,以识别管道或内存停顿;注意,分支繁重的代码可能会受到闪存获取延迟的限制——将热循环重新定位到SRAM或启用加速模式通常会显著提高归一化得分。

内存和I/O吞吐量:RAM带宽、DMA和外围设备压力

点:存储器和外的吞吐量的定义持续的运动的数据的性能。 证据:测量memcpy吞吐量变化的传输大小,DMA持续MB/s下并发CPU负荷和周围爆率为SPI/串口. 说明:图吞吐量vs转的大小,以找到交叉点DMA优于CPU驱动的转让;日志CPU利用在转移到揭示了空间应用处理移动时的数据。

功耗和效率分析(方法指南)

主动、空闲和低功耗模式测量

要点:跨模式功耗分析揭示了可用的节能空间。证据:包括全负载活动(最大时钟+外设)、时钟门控空闲状态和深度睡眠模式;通过测量电流和轨电压计算功耗(mW),并在稳定窗口内取平均值。解释:避免单次样本快照——在重复周期内取平均值并捕捉瞬态变化;记录测量分辨率和采样方法;提供一个电流、电压和计算功耗的表格模板,以确保报告的可比性。

| 模式 | 当前(mA) | 电压 (V) | 功率 (mW) |

|---|---|---|---|

| 活动(最大) | — | — | - |

| 闲置 | — | — | — |

| 深度睡眠 | — | — | — |

Energy-per-operation和权衡(功率与性能)

要点:每操作能量统一了功率和延迟权衡。证据:计算E=功率×每操作时间,并在扫描时钟或DVFS(如果可用)时绘制能量与吞吐量。解释:降低时钟通常会降低绝对功率,但如果执行时间增长超过功率下降,则可能会增加每项任务的能量;实用技巧包括使用DMA、批处理I/O和减少唤醒以最大限度地减少每项任务的能量。

吞吐量测试:以太网、DMA与真实案例研究(案例研究+方法)

以太网及网络吞吐量测试计划与解读

要点:网络测试必须隔离协议和CPU开销。证据:使用不同大小的数据包运行TCP/UDP流,交替使用中断驱动与零拷贝方法,并测量丢包率、抖动和每Mbps的CPU开销。解释:呈现吞吐量与数据包大小的关系以及CPU负载与吞吐量的关系,以识别中断或缓冲区处理成为CPU瓶颈的点;量化每个数据包的CPU周期,以指导缓冲区大小调整和中断合并。

小型案例研究 + 部署清单(实际应用调优)

要点:实际调优可带来可测量的吞吐量和效率提升。证据:在一个传感器聚合网关示例中,应用优先级DMA通道、中断分组和调整缓冲区大小,提升了持续MB/s并降低了CPU负载。解释:部署清单 — 优先将稳定流迁移到DMA,将延迟敏感代码放在SRAM中,启用外设批处理,选择合适的睡眠模式,并添加CPU、内存和电流的运行时监控以检测现场中的回归问题。

摘要 & 可执行要点 (10‑15% 的文章)

要点:衡量的优势和限制指导集成选择xmc4800e196k2048最大功率1.证据:当热代码在SRAM和使用FPU加速数学时,测试显示出强大的DMA支持的吞吐量和可靠的每瓦计算。解释:工程师应该首先运行一个轻量级的CoreMark加上memcpy和DMA吞吐量测试,然后应用优先级DMA、缓冲区调整和中断分组以达到可用的以太网和I/O性能。

- 首先运行CoreMark和memcpy微基准测试,以建立基准CoreMark/MHz和RAM带宽;这些数字预测了的原始计算和数据移动扩展空间xmc4800e196k2048最大功率1.

- 使用 DMA 进行持续传输,并将延迟敏感的循环重定位到 RAM 中,以减少闪存停滞效应并提高在真实中断情况下的标准化吞吐量。

- 测量每操作的能耗以平衡时钟降低与运行时间增加;批量I/O并减少唤醒次数以降低电池受限部署中的μJ/op。

常见问题解答

我应该首先运行哪个基准进行对比评估?

从固定时钟的CoreMark和一个小的memcpy微基准开始,以捕获CPU基线和RAM带宽。这两个快速测试揭示了设备是CPU还是内存受限,并指导是否优先考虑代码重定位、DMA或时钟调整以进行进一步的分析。

我应该如何测量可重复结果的功率?

使用校准过的并联电阻和采样的ADC或高侧功率计,在多次运行中平均,并在唤醒时用示波器捕捉瞬态。记录环境条件、轨道解耦和采样分辨率,以确保不同设备间的测量数据可比。

哪种调优可以获得最大的吞吐量增益?

将稳态传输移至DMA并调整缓冲区大小以匹配以太网数据包突发通常提供最大的持续MB/s改进,同时为应用程序逻辑释放CPU。将此与中断合并相结合,并将热循环置于SRAM以获得最佳结果。